# 實驗七 正反器 (Flip - Flop)

## 一・ 實驗器材

| 名稱      | 數量 | 名       | 稱 | 數量 |

|---------|----|---------|---|----|

| IC 7400 | 1  | IC 7476 |   | 1  |

| IC 7402 | 1  | LED     |   | 2  |

| IC 7474 | 1  |         |   |    |

## 二・ 預習作業

- 1. 由 I.C.手册查出 7402 的結構及其特性。

- 2. 由 I.C. 手冊查出 7474 及 7476 的構造及特性。

- 3. 說明 R-S 正反器的工作原理。

- 4. 說明 "FLIP-FLOP" 的工作原理。

- 5. I.C. 7474 及 7476 中均有 Clear 及 Preset 二接腳, 說明 Clear 及 Preset 的作用。

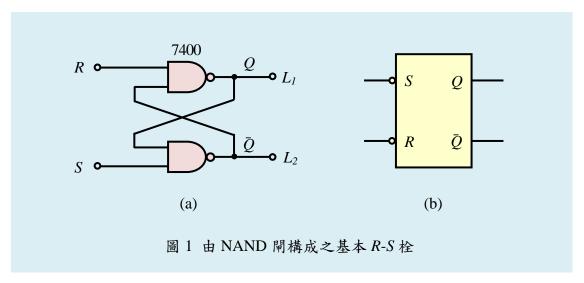

## 工作一:基本R-S栓

1. 圖 1(a)是沒有時脈輸入之基本 R-S latch,按圖 1(a) 接妥電路,Q、 $\overline{Q}$  接 HI/LOW 指示器,S、R 接 HI/LOW 信號輸出(LED), 7400 的第 14 腳接電源 5V,第 7 腳接地。圖 1(b) 則為 R-S latch 之電路符號。

- 2. 依表 1 所示的組合,將 S 與 R 分別接 HI/LOW 信號,並記錄 Q ,  $\overline{Q}$  ( $L_1$  ,  $L_2$ )的輸出指示於表中。

- 3. 讓圖 1 的電路 R 接 HI,觀察 S 的信號改變對輸出有何影響?

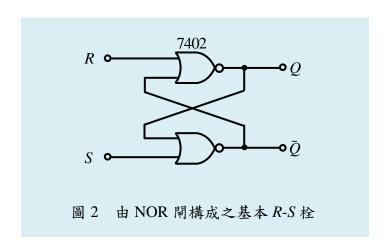

- 4. 如圖 2,將圖 1 中的 NAND 閘改成 NOR 閘而後重覆步驟 1-3,將結果填於表 2。

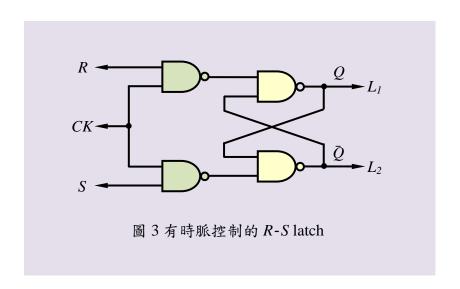

5. 圖 3 是附有時脈控制的 R-S latch,整個電路由一個 7400 組成。

6. 依表 3 所示的組合,將 S,R,CK 分別接 HI/LOW 信號輸出,並記錄 Q, $\overline{Q}$   $(L_1$ , $L_2$ ) 的輸出指示於表中。

## 工作二:D型正反器

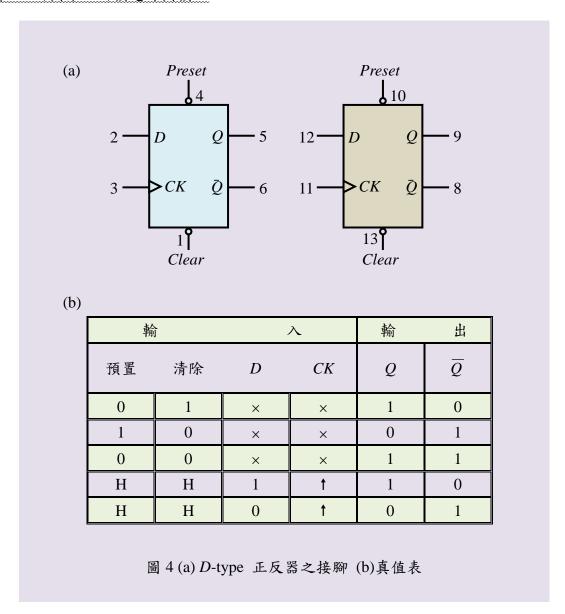

7474 為常用的 TTL D型正反器,此 IC 屬於正緣觸發正反器,其接腳與真值表如圖 4 所示,第 14 腳與第 7 腳接電源與接地。

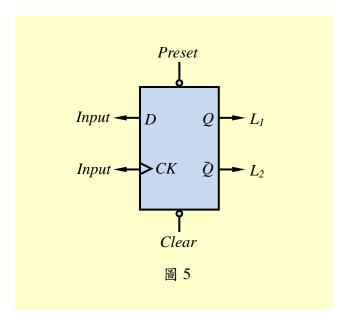

- 取 1/2 7474 按圖 5 接妥電路,輸入端 D 與 CK 空接, Clear (清除) 接 HI, Preset (預置)接 LOW,輸出 Q 為 \_\_\_\_\_\_,任意變化 D 與 CK 之輸入,輸出 Q 會改變嗎? \_\_\_\_\_\_。

再將輸入端 D 與 CK 空接,把 Clear 改接 LOW, Preset 接 HI,輸出 Q 為 \_\_\_\_\_\_,

任意變化 D 與 CK 之輸入,輸出 Q 會改變嗎? \_\_\_\_\_。

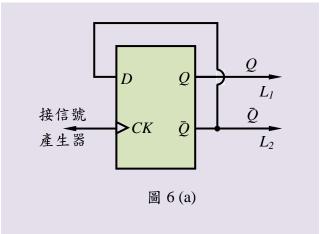

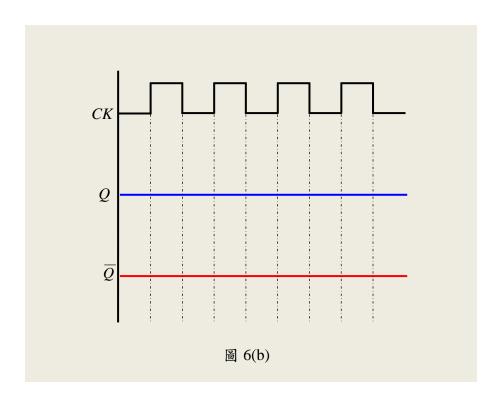

- 2. 將 Preset、Clear 接 HI, 按圖 6(a)插妥電路, 輸入 CK 接信號產生器 (OUTPUT/TTL),

繪出Q與 $\overline{Q}$ 的相對應輸出變化於圖6(b)。

## 工作三:J-K正反器:

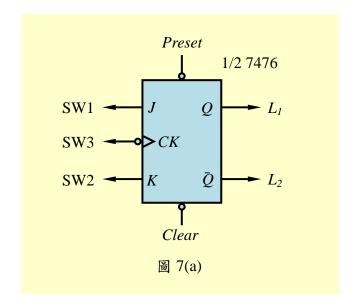

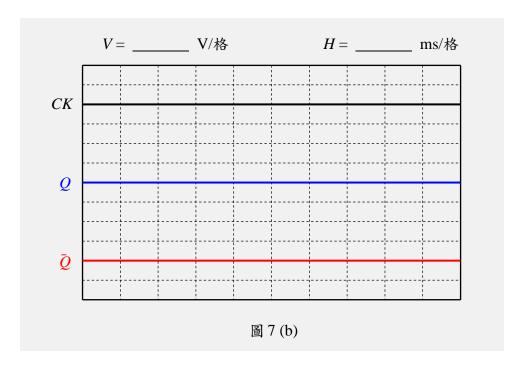

- 取 1/2 7476 按圖 7(a) 插妥電路, Clear, Preset 接 HI。SW1, SW2 接於 HI, SW3 接信號產生器(OUTPUT/TTL), 輸出頻率約 50 Hz 之方波,以示波器觀察,紀錄 CK 的頻率, Q 的頻率, Q 的頻率,並將波形繪於圖 7(b) 中,觀察 CK 由 HI 到 LOW 時, Q 的改變情形,是屬於何種觸發?(此電路可當作 T 型正反器。)

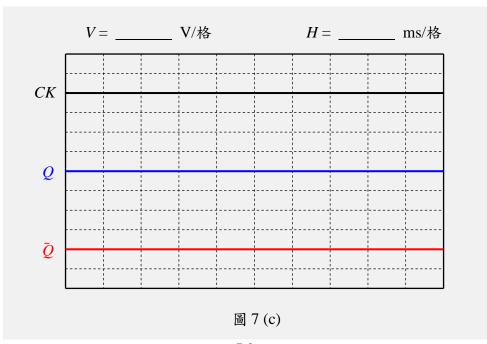

- 2. 調整信號產生器上的 Duty 鈕(拉出旋鈕調整)使輸出的方波形的 HI / LOW 寬度不同, 比值約為 2:1,用示波器觀察 Q 與  $\overline{Q}$  的波形,其 HI / LOW 寬度是否相同?將結果繪 於圖 7(c)中。

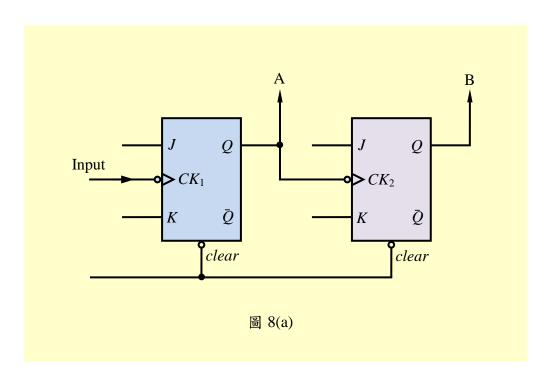

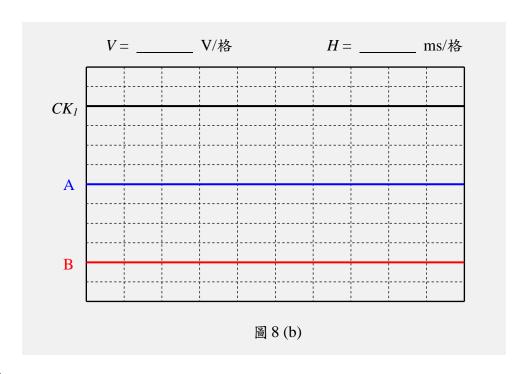

- 3. 如圖 8(a)接好線路,Clear、Preset 接 HI,調整信號產生器使其輸出頻率為 f=300 Hz 之方波接於  $CK_1$ ,用示波器量測  $CK_1$  的輸入頻率  $f_{CK}$  ,A 點的輸出頻率  $f_A$ ,B 點的輸出頻率  $f_B$ ,並繪出  $CK_1$  與 A、B 點的波形於圖 8(b) 中。

## 實驗七 正反器

| 組別: | 學號:   | 姓名: | 同組同學姓名: |

|-----|-------|-----|---------|

| 日期: | 教師簽署: |     |         |

## -、基本R-S栓

表 1 基本 R-S latch 真值表

| 輸 | λ | 輸出        |                      |  |  |

|---|---|-----------|----------------------|--|--|

| R | S | $Q = L_1$ | $\overline{Q} = L_2$ |  |  |

| 0 | 1 |           |                      |  |  |

| 1 | 1 |           |                      |  |  |

| 1 | 0 |           |                      |  |  |

| 1 | 1 |           |                      |  |  |

| 0 | 0 |           |                      |  |  |

表 2 基本 R-S latch 真值表

| 輸 | λ | 輸出 |                |  |  |

|---|---|----|----------------|--|--|

| R | S | Q  | $\overline{Q}$ |  |  |

| 0 | 1 |    |                |  |  |

| 0 | 0 |    |                |  |  |

| 1 | 0 |    |                |  |  |

| 0 | 0 |    |                |  |  |

| 1 | 1 |    |                |  |  |

表 3

有時脈 R-S latch 真值表 (CK = 1) 有時脈 R-S latch 真值表 (CK = 0)

| 車 | 渝 ノ |    | 輸 | 出              | 車 | 渝 ノ |    | 輸 | 出              |

|---|-----|----|---|----------------|---|-----|----|---|----------------|

| R | S   | СК | Q | $\overline{Q}$ | R | S   | СК | Q | $\overline{Q}$ |

| 0 | 1   |    |   |                | 0 | 1   |    |   |                |

| 0 | 0   |    |   |                | 0 | 0   |    |   |                |

| 1 | 0   |    |   |                | 1 | 0   |    |   |                |

| 0 | 0   |    |   |                | 0 | 0   |    |   |                |

| 1 | 1   |    |   |                | 1 | 1   |    |   |                |

### 二、D 型正反器

1. 圖 5 中,當 Preset 或 Clear 接 LOW 時(但不可同時為 LOW),任意變化 D 與 CK 之輸入,輸出 Q 會改變嗎? \_\_\_\_\_。這表示此二者之優先權較 D 為 \_\_\_\_\_(高或低)。

### 2. 圖 6(b):

3. 觀察 Q 隨 CK 之變化,知其屬於\_\_\_\_\_\_觸發。

#### 三、J-K正反器

按圖 7(a),輸出頻率約 50 Hz 之方波, CK 的頻率 \_\_\_\_\_ Hz, Q 的頻率 \_\_\_\_\_ Hz, Q

的頻率 \_\_\_\_\_ Hz, 是屬於 \_\_\_\_\_ 觸發。

2. 輸入波形 CK 的 HI / LOW 寬度不同時, Q 與  $\overline{Q}$  的波形 HI / LOW 寬度是否相同? \_\_\_\_\_。 Q 的波形 HI / LOW 比為 \_\_\_\_\_,  $\overline{Q}$  的波形 HI / LOW 比為 \_\_\_\_\_,

3. 圖 8(a) 中 , $f_{A}:f_{B}=$ \_\_\_\_\_, $f_{B}:f_{CK}=$ \_\_\_\_\_, $f_{A}:f_{CK}=$ \_\_\_\_。

四、問題

1. 表1與表2有何不同?

2. 圖 1 的電路 R 接 HI 時, S 的信號改變對輸出有何影響?

3. 由表 3 中可發現,唯有 CK 在 \_\_\_\_\_\_ 時,R-S latch 的輸出才會改變,因此電路的 R , S 輸入是 \_\_\_\_\_\_ (高態或低態) 動作。

- 4. 說明 R-S 栓 (圖 1(a)) 之原理, CK (圖 3) 加入後有何作用?

- 5. 以邏輯閘符號繪出 D 正反器之構造,並與 R-S 栓比較。

- 6. 何謂「正緣」、「負緣」觸發?

- 7. 舉一實例,說明正反器之應用。

#### 五、討論